2024-12-20

ALINX 正式發(fā)布 AMD Virtex UltraScale+ 系列 FPGA PCIe 3.0 綜合開發(fā)平臺(tái) AXVU13P!

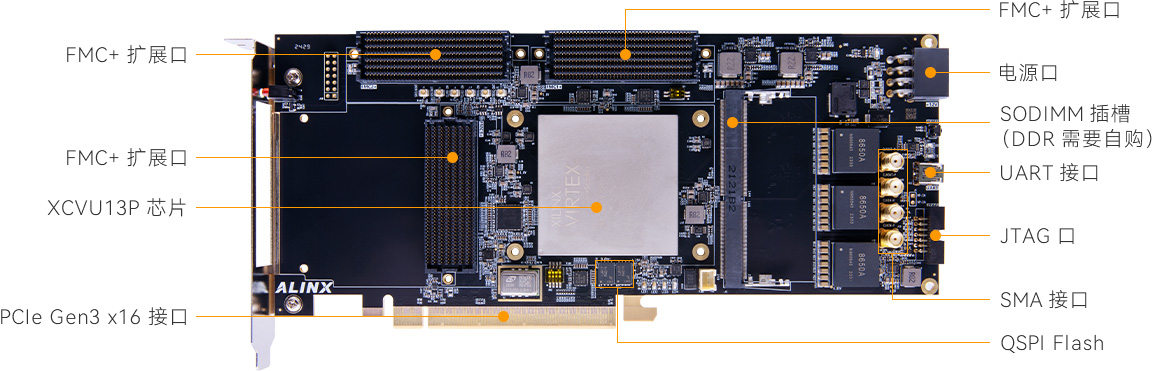

這款搭載 AMD 16nm 工藝 XCVU13P 芯片的高性能開發(fā)驗(yàn)證平臺(tái),憑借卓越的計(jì)算能力和靈活的擴(kuò)展性,專為應(yīng)對(duì)復(fù)雜應(yīng)用場(chǎng)景和高帶寬需求而設(shè)計(jì),助力技術(shù)開發(fā)者加速產(chǎn)品創(chuàng)新與部署。 隨著 5G、人工智能和高性能計(jì)算等領(lǐng)域的迅猛發(fā)展,各行業(yè)對(duì)計(jì)算能力、靈活性和高速數(shù)據(jù)傳輸?shù)男枨蟪掷m(xù)攀升。FPGA 憑借其高度可編程性和實(shí)時(shí)并行處理能力,已成為解決行業(yè)痛點(diǎn)的關(guān)鍵技術(shù)。ALINX 此次推出的基于 AMD Virtex UltraScale+ FPGA PCIe 3.0 綜合開發(fā)平臺(tái),在性能和功能上都達(dá)到了新的高度,以強(qiáng)大的算力、高速通信能力和靈活擴(kuò)展性,全面賦能行業(yè)創(chuàng)新。 5G 基站與網(wǎng)絡(luò)加速 平臺(tái)擁有 76 個(gè) GTY 高速收發(fā)器,支持速率高達(dá) 28.21 Gb/s,輕松應(yīng)對(duì) 5G 基站和網(wǎng)絡(luò)通信中的高帶寬和低延遲需求。3 路 FMC+ 接口讓外接模塊擴(kuò)展更加便捷,滿足前沿通信技術(shù)發(fā)展的復(fù)雜需求。 人工智能與機(jī)器學(xué)習(xí) XCVU13P 芯片擁有 378 萬(wàn)邏輯單元和 38.3 TOPS 的 INT8 DSP 峰值性能,為深度學(xué)習(xí)推理和訓(xùn)練任務(wù)提供強(qiáng)勁動(dòng)力。它是數(shù)據(jù)中心 AI 加速的理想選擇,也適用于邊緣計(jì)算中對(duì)算力和功耗的平衡需求。 工業(yè)控制與測(cè)試測(cè)量 通過(guò) 12,288 個(gè) DSP 切片,這款平臺(tái)能處理復(fù)雜的信號(hào)處理任務(wù),支持精密測(cè)量和實(shí)時(shí)控制場(chǎng)景,助力工業(yè) 4.0 智能制造的全面升級(jí)。 接口方面,AXVU13P 采用的 PCIe 3.0 x16 接口提供每通道 8 Gbps 的通信速率,為客戶的多任務(wù)需求保駕護(hù)航。采用 1 個(gè)支持容量高達(dá) 16GB 的 DDR4 SODIMM 內(nèi)存條插槽,允許用戶根據(jù)需求自行選擇和安裝內(nèi)存,以應(yīng)對(duì)不同規(guī)模的數(shù)據(jù)高速處理。 3 路 FMC+ 接口支持高達(dá) 56 通道的 GTY 高速收發(fā)器,可以連接各種標(biāo)準(zhǔn)的 FMC 和 FMC+ 模塊,為用戶帶來(lái)更多靈活性和可擴(kuò)展性。2 路 128MB QSPI Flash、2 路 SMA 輸入輸出接口、1 路 UART 轉(zhuǎn) USB 接口等多種擴(kuò)展接口,讓開發(fā)更加靈活,從原型設(shè)計(jì)到量產(chǎn)一步到位。

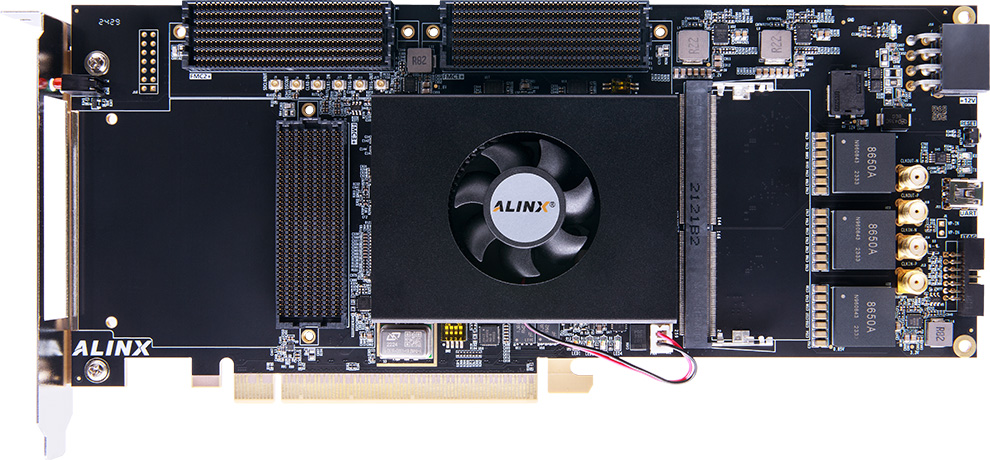

(AMD Virtex UltraScale+ 系列 FPGA PCIe 3.0 綜合開發(fā)平臺(tái) AXVU13P) 該平臺(tái)的應(yīng)用場(chǎng)景覆蓋多個(gè)前沿領(lǐng)域。在 5G 基站和網(wǎng)絡(luò)加速,雷達(dá)系統(tǒng)、測(cè)試與測(cè)量,以及機(jī)器學(xué)習(xí)、AI 推理、仿真與原型設(shè)計(jì)等領(lǐng)域,AXVU13P 都能憑借其卓越的性能和靈活性,為行業(yè)技術(shù)突破提供可靠基礎(chǔ)。